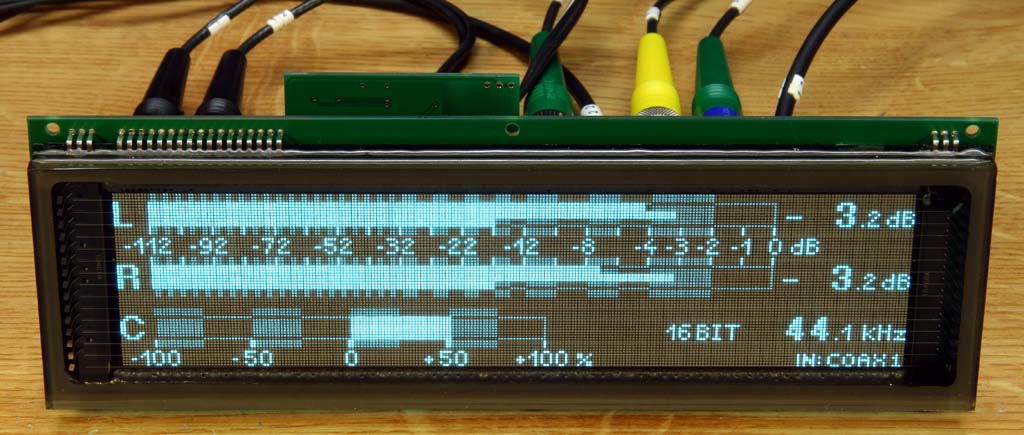

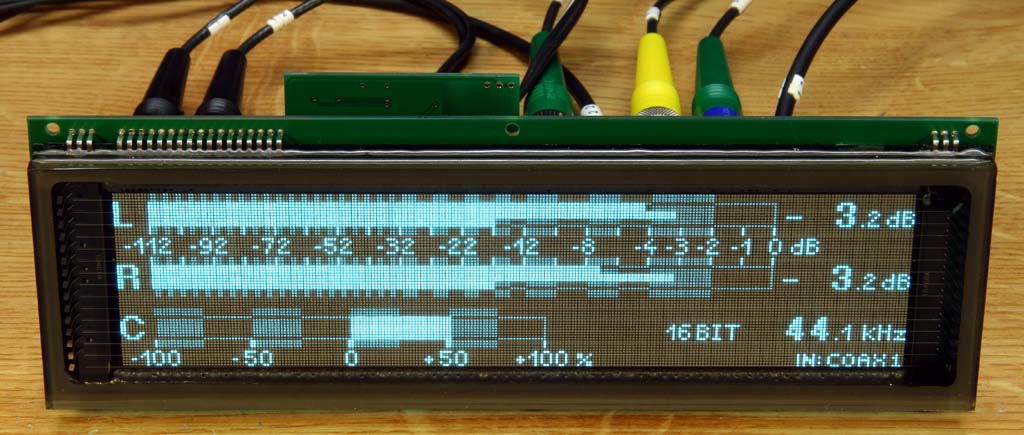

Anlass für diese Entwicklung war, dass ich zum Einen ein paar herrliche, grafische VFDs zur Verfügung hatte, die ich unbedingt in Funktion sehen wollte. Darüber hinaus hatte ich glücklicherweise auch eine echte und interessante Anwendung dafür. So ist das "DPLCM-VFD" entstanden, "DPLCM" steht für "Digital Audio Peak Level and Correlation Meter".

Auf Jogis Röhrenseite soll natürlich das VFD im Vordergrund stehen, denn das ist ja auch eine Röhre. Mit geheizter Kathode, Gittern und Anoden, nur eben ganz flach und überhaupt nicht rund wie eine Röhre. Also fange ich mit dem VFD an und erzähle dann noch etwas vom Rest des Gerätes. Letzteres ist auch ausführlich in dem englischsprachigen Artikel "A VFD-equipped Digital Audio Peak Level and Correlation Meter with many Extra Functions" beschrieben.

Das Display ist ein MN25664P von Noritake-Itron. Die wichtigsten technischen Daten sind:

Insbesondere die Logik-Versorgungsspannung von 3,3 V und die 16 darstellbaren Helligkeitsstufen sind unüblich. Ich habe nur noch ein weiteres, vergleichbares Display mit diesen Eigenschaften gefunden (MN25664M, auch 256 x 64 Pixel, aber 0,45 mm Dot Pitch). Die Daten des MN25664P sind nicht auf der Noritake Webseite zu finden.

Optisch finde ich ein VFD in dieser Anwendung schlicht und ergreifend "schöner" oder meinetwegen auch "faszinierender". Verglichen mit LC-Displays, insbesondere den kleineren Versionen für den Industriebedarf, dürfte der technische Vorteil eines VF-Displays hier hauptsächlich in dessen außerordentlich kurzer Ansprechzeit (wie bei Bildröhren) liegen, die kombiniert mit 150 Hz Bildwiederholzeit besonders gut zum Tragen kommt.

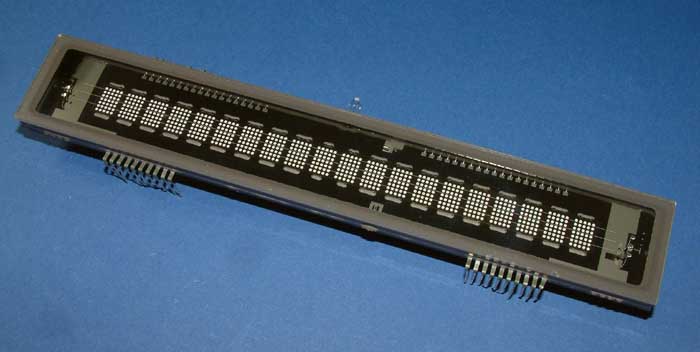

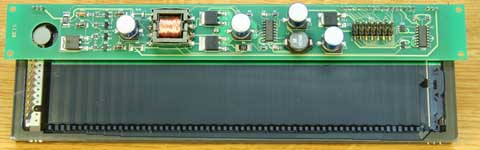

Zurzeit

habe ich zwei Aufbauvarianten. In beiden Fällen ist eine

Leiterplatte direkt hinter dem Display montiert (mit doppelseitigem

Klebeband - selbst bei Noritake weiß man nichts Geeigneteres)

und das Display ist direkt in die Leiterplatte eingelötet.

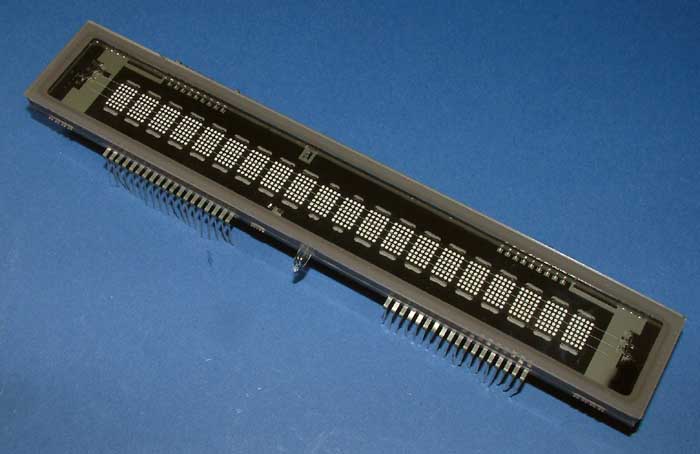

Zurzeit

habe ich zwei Aufbauvarianten. In beiden Fällen ist eine

Leiterplatte direkt hinter dem Display montiert (mit doppelseitigem

Klebeband - selbst bei Noritake weiß man nichts Geeigneteres)

und das Display ist direkt in die Leiterplatte eingelötet.

Auf die Bilder für eine vergrößerte Ansicht klicken.

Die Baugruppe "VFD-PS" (rechts) enthält nur die Versorgung des VFDs mit DC-DC-Wandler und Sicherheitsschaltungen. Die Schnittstelle zur VFD-Ansteuerung ist herausgeführt, die ganze "Intelligenz" zur Erzeugung des VFD-Ansteuersignals und dessen Inhalt muss außerhalb realisiert werden.

Die

Baugruppe "VFD-MB" (links) enthält die gleiche

Versorgung des VFDs wie bei der VFD-PS, darüber hinaus noch

ein FPGA samt den für das FPGA minimal notwendigen Zusatzbauelementen.

Das FPGA kann nicht nur für die gesamte VFD-Ansteuerung übernehmen,

sondern es kann auch die Applikation enthalten, wie hier im DPLCM

die Logik für ein komplexes Aussteuerungsmessinstrument.

Die

Baugruppe "VFD-MB" (links) enthält die gleiche

Versorgung des VFDs wie bei der VFD-PS, darüber hinaus noch

ein FPGA samt den für das FPGA minimal notwendigen Zusatzbauelementen.

Das FPGA kann nicht nur für die gesamte VFD-Ansteuerung übernehmen,

sondern es kann auch die Applikation enthalten, wie hier im DPLCM

die Logik für ein komplexes Aussteuerungsmessinstrument.

Viele der I/O-Leitungen des FPGAs sind heraus geführt, und was extern daran angeschlossen wird, liegt nicht fest. In meinem Fall sind das die notwendigen Zusatzschaltungen, hauptsächlich die digitalen Audio-Ein- und Ausgänge, für ein Audio-Pegelmessgerät. Es könnte aber auch ein Wetterempfänger oder die Leistungstreiber und Tastaturanschlüsse für eine Waschmaschine oder was auch immer sein. Im einfachsten Fall könnte das FPGA so programmiert werden, dass sich die ganze Baugruppe wie ein Bildwiederholspeicher-RAM mit 256 x 64 Worten je 4 Bit, also 14 Adress- und 4 Datenbits, CS und R/W, verhält.

Als

Röhre braucht das VFD eine Heizspannung und eine Anodenspannung.

Beide werden aus einem Gegentaktwandler mit ca. 120 kHz erzeugt.

Außerdem wird die Betriebsspannung der eingebauten Halbleiterlogik

benötigt.

Hier oder auf die nebenstehende Grafik für die Gesamtschaltung klicken.

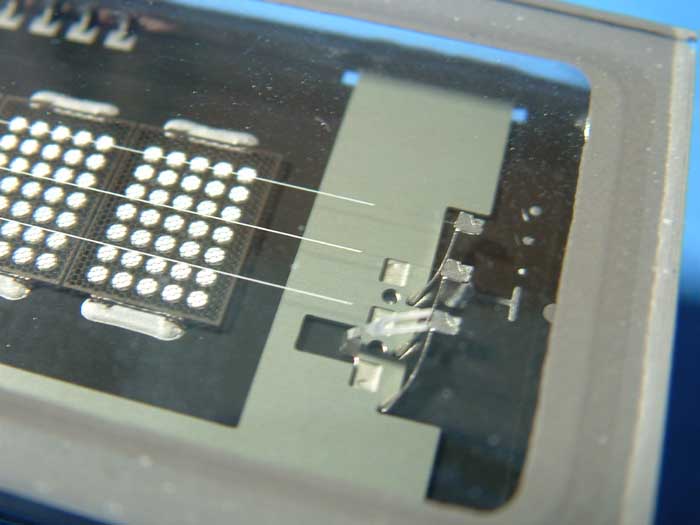

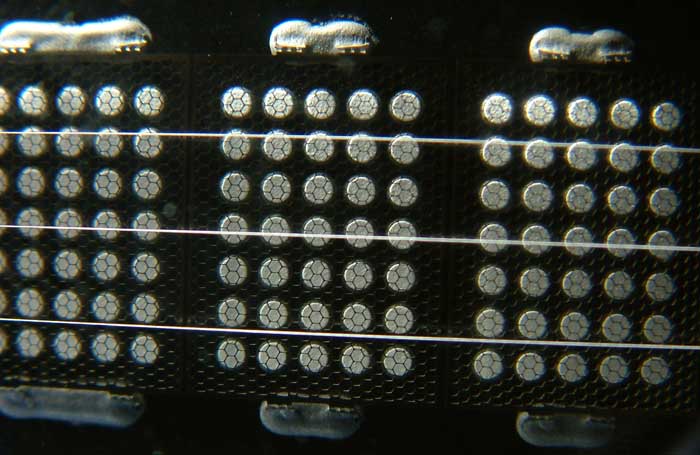

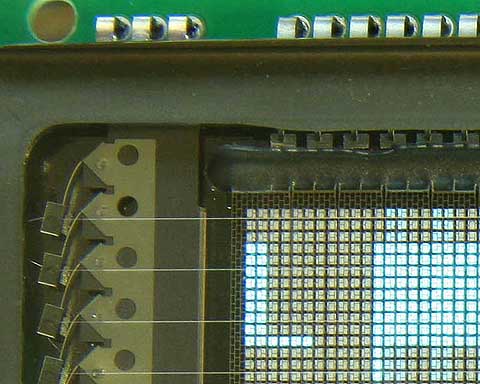

Die Kathode ist direkt geheizt und besteht aus 16 horizontal federnd vorgespannt aufgehängten Drähten. Sie sind besonders gut auf dem Fotos weiter unten zu erkennen. Damit die Gitterspannung, die minimal 0 V annehmen kann, negativ gegenüber der Kathode werden kann, muss die Kathode einige Volt über der Masse liegen, bei mir sind das +12 V. Außerdem soll sie mit Wechselspannung betrieben werden und beide Enden der Drähte sollen im Gegentakt symmetrisch angesteuert werden, damit die Heizspannung, die ja bei Direktheizung die Spannungsdifferenz zum Gitter mit bestimmt, möglichst geringen Einfluss auf die Helligkeit hat.

Die Anodenspannung soll ca. 55 V betragen. Sie wird in dieser Versorgungsschaltung sogar stabilisiert. Jedes Pixel stellt eine Anode dar, die im gemultiplexten Betrieb einzeln ein- oder ausgeschaltet wird (wobei die Treiber dazu, wie gesagt, im VFD sind). Der Gesamt-Anodenstrom liegt bei bis zu ca. 75 mA.

Logik-Versorgungsspannung von 3,3 V wird extern durch einen Linearregler aus der Geräteversorgungsspannung von 12 V erzeugt.

Sicherheitsschaltung: Bei Fehlern in der Spannungsversorgung oder Ansteuerung kann leicht das VFD beschädigt oder zerstört werden. Zwei Sicherheitsschaltungen sollten vorgesehen werden:

Zum einen sollte das Display dunkel geschaltet werden, wenn der Multiplex-Prozess stehen bleibt: ähnlich einer Bildröhre, bei der der Strahl nicht mehr abgelenkt wird, kann es zum Einbrennen kommen. Dazu prüft Sicherheitsschaltung mit einem wieder-triggerbaren Monoflop, ob Daten aus dem Schieberegister für die Ansteuerung heraus kommen. Mit hinreichender Sicherheit und Geschwindigkeit kann daraus geschlossen werden, ob der Multiplexprozess läuft oder nicht und ggf. kurzfristig ausgeschaltet werden.

Sehr viel kritischer als mögliches Einbrennen ist, wenn die Logik-Versorgungsspannung nicht oder nicht ausreichend vorhanden ist, bevor die Anodenspannung ansteht. Die Anodenspannung kann dann in den Digitalteil "eindringen" (fragt mich nicht, wie), und den zerstören. Das ist ein Nachteil der CIG-Technologie: Dann ist das ganze Display Schrott und nicht nur ein IC. Als Schutzschaltung ist ein Spannungsüberwachungs-IC vorgesehen, das in sehr kurzer Zeit die Anodenspannung abschalten kann. Ich habe einige Male Blut und Wasser geschwitzt, weil ich nach einem Versehen angenommen hatte, dass die Sicherheitsschaltung versagt hätte und das Display zerstört wäre - aber bislang haben alle Displays bisher alles überstanden.

Die

Ansteuerung des VFDs ist, gelinde gesagt, "verwirrend".

Es hat mich eher Tage als Stunden gekostet, zu verstehen, was

zu machen ist, und erst als ich kapiert hatte, wie das Display

aufgebaut ist, habe ich die wirren Angaben des Datenblatts eingesehen

und verstanden. Zu erklären, wie die Ansteuerung funktioniert,

ist eine echte Herausforderung. Eigentlich müsste man einen

Film mit Animationen dazu anfertigen. Zu versuchen, das Thema

in ein paar Textzeilen, ohne Grafiken zusammenzufassen, ist aussichtslos,

was mich nicht davon abhält, es trotzdem zu tun.

Die

Ansteuerung des VFDs ist, gelinde gesagt, "verwirrend".

Es hat mich eher Tage als Stunden gekostet, zu verstehen, was

zu machen ist, und erst als ich kapiert hatte, wie das Display

aufgebaut ist, habe ich die wirren Angaben des Datenblatts eingesehen

und verstanden. Zu erklären, wie die Ansteuerung funktioniert,

ist eine echte Herausforderung. Eigentlich müsste man einen

Film mit Animationen dazu anfertigen. Zu versuchen, das Thema

in ein paar Textzeilen, ohne Grafiken zusammenzufassen, ist aussichtslos,

was mich nicht davon abhält, es trotzdem zu tun.

Für den "normalen" Leser, der sich wohl niemals mit der Ansteuerung abplagen will oder muss, ist dieses Kapeitel aber ohne Belang und sollte übersprungen werden.

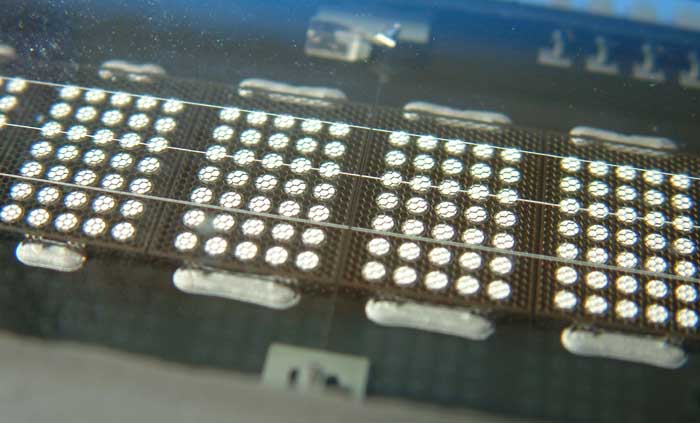

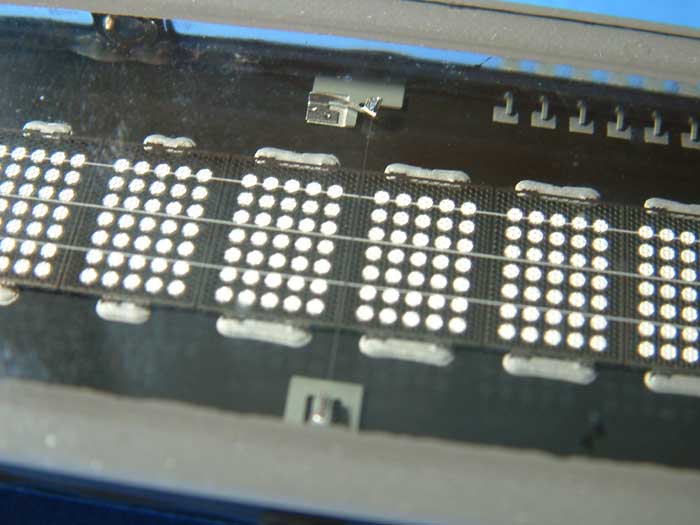

Das Display hat 64 Zeilen je 265 Pixel. Es arbeitet gemultiplext mit einer Rate von 1 : 63, d. h., maximal 256 Pixel leuchten gleichzeitig. Wer jetzt glaubt, das ist doch ganz einfach, jeweils die 256 Pixel einer Zeile leuchten gleichzeitig, ist schonmal auf dem Holzweg. Das geht technologisch offensichtlich nicht: Man müsste 64 Gitter bauen, die je eine Zeile betreiben - gaaaanz lang und gaaaanz dünn. Vielleicht mit 64 langen Drähten, aber das wird aus sicherlich gutem Grunde nicht gemacht.

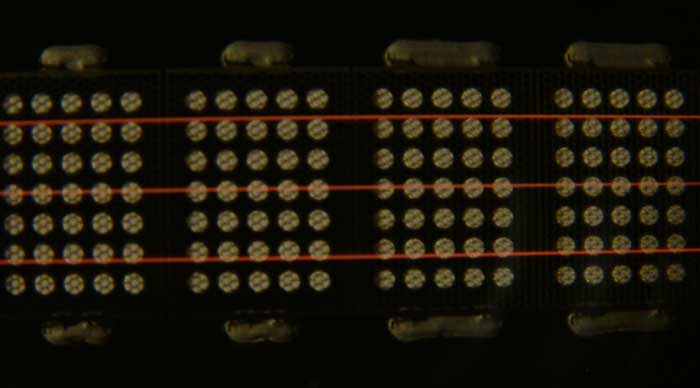

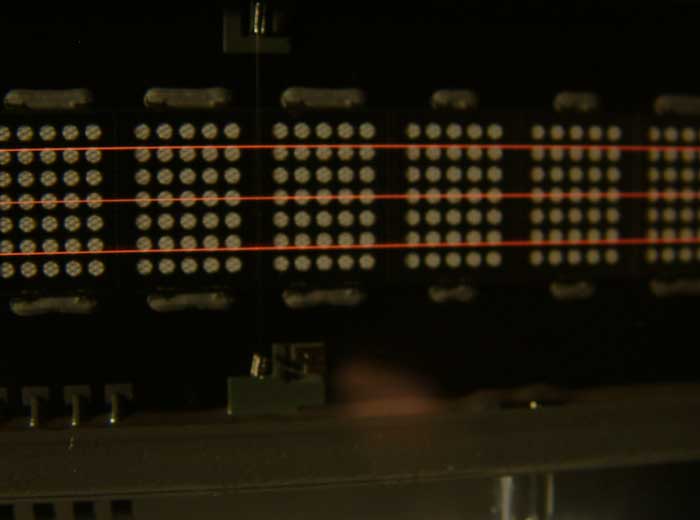

Statt dessen gibt es 64 Gitter, die je einen Block von 4 Pixeln über 64 Zeilen, also wieder 256 Pixel, abdecken. 5 der 64 Gitter sind auf dem Foto rechts zu erkennen (große Gesamtansicht 1600 Pixel hier). Und noch einmal: Wer jetzt denkt, das ist doch auch ganz einfach, jeweils die 256 Pixel eines Blockes leuchten gleichzeitig, ist schon wieder auf dem Holzweg. das Problem ist, dass die Gitter nicht randscharf arbeiten, dass also Pixel auch von benachbarten Gittern beeinflusst werden. Deshalb werden immer jeweils zwei nebeneinander liegende Gitter gleichzeitig eingeschaltet (512 Pixel), und per Ansteuerlogik wird dafür gesorgt, dass nur die Anoden der inneren 4 Spalten eingeschaltet werden. Die 4 Spalten im Randbereich bleiben immer ausgeschaltet.

Die Daten, um die einzelnen Anoden und Gitter zu aktivieren werden seriell in ein Schieberegister geschoben. Pro Multiplexphase sind 256 Pixeldaten und 64 Gitterdaten zu übertragen (wie die Pixel lassen sich auch die Gitter mit 64 Bit alle einzeln ansteuern, obwohl immer nur ein Päärchen in Betrieb ist, für das auch ein 6-Bit-Wert ausreichen würde). Mein Running Gag: Wer jetzt denkt, das ist doch auch noch nicht so schlimm, jeweils die 256 Pixel eines solchen "Doppel-Halbblocks" schön der Reihe nach, Pixel für Pixel, Zeile für Zeile übertragen, sieht sich schon wieder getäuscht.

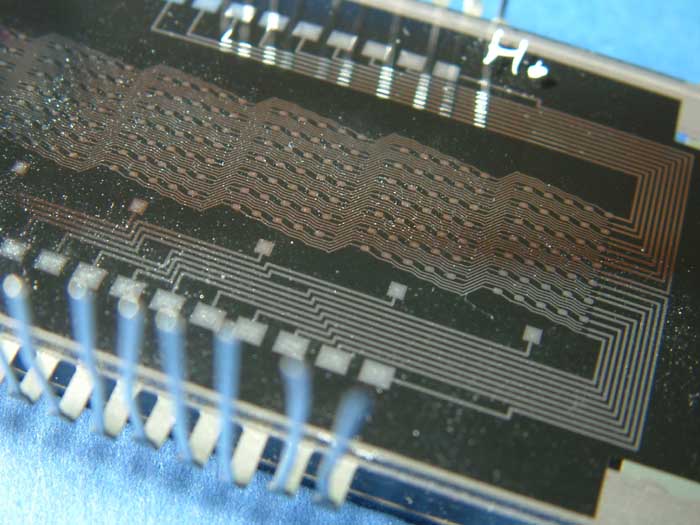

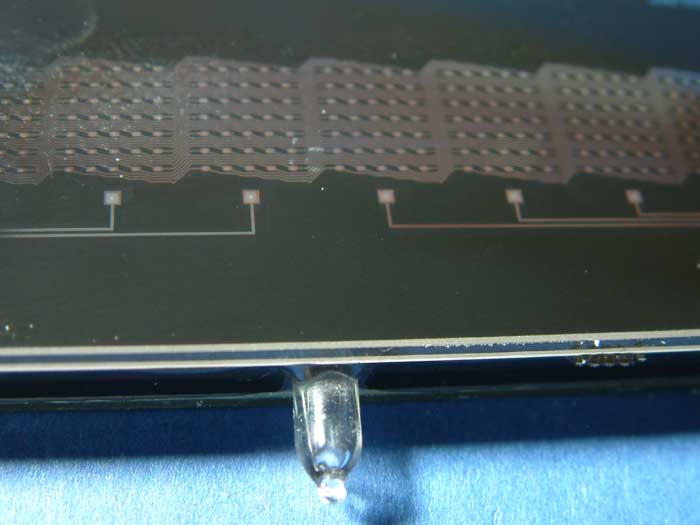

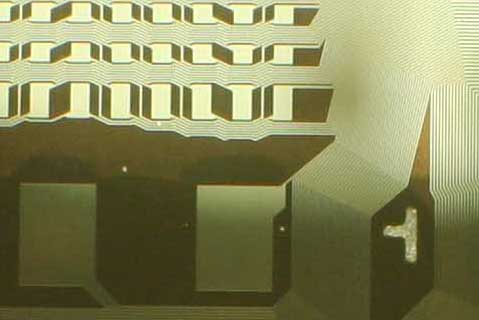

Dazu

das Foto vom "Routing" der Anoden, das von hinten durch

die gläserne Rückwand sichtbar ist: Aufgrund der "sehr

beengten" Platzverhältnisse zum Verbinden der Anoden

kehrt sich die Reihenfolge der Anoden alle 8 Pixel um. Zur Erinnerung:

Wenn zwei Gitter gleichzeitig eingeschaltet sind, könnten

8 Pixel pro Zeile leuchten. 4 dürfen aber nur leuchten, die

anderen müssen ausgeschaltet bleiben. Obwohl nur 4 leuchten,

müssen die Anoden in 8er-Gruppen parallel geschaltet werden,

also müssen pro Display-Zeile 8 Leitebahnen horizontal laufen,

7 Leiterbahnen zwischen zwei Anodenkontakten im 0,635 mm-Raster

hindurch. Da lässt sich keine einfache Reihenfolge a-b-c-d-e-f-g-h

- a-b-c-d-e-f-g-h einhalten. Die Leiterbahnen auf dem Foto sind

im ca. 45 µm-Raster, also geschätzt bei 15 µm

Abstand nur 30 µm breit. Zur Verkomplizierung der Ansteuerung

kommt hinzu, dass, obwohl 512 Anoden pro Multiplexphase anzusteuern

sind, nur 256 Anodendaten übertragen werden, aber eine externe

Information (das Signal "DTENA") bestimmt, welcher der

256er-Gruppe gemeint ist. Ist halt nicht trivial.

Dazu

das Foto vom "Routing" der Anoden, das von hinten durch

die gläserne Rückwand sichtbar ist: Aufgrund der "sehr

beengten" Platzverhältnisse zum Verbinden der Anoden

kehrt sich die Reihenfolge der Anoden alle 8 Pixel um. Zur Erinnerung:

Wenn zwei Gitter gleichzeitig eingeschaltet sind, könnten

8 Pixel pro Zeile leuchten. 4 dürfen aber nur leuchten, die

anderen müssen ausgeschaltet bleiben. Obwohl nur 4 leuchten,

müssen die Anoden in 8er-Gruppen parallel geschaltet werden,

also müssen pro Display-Zeile 8 Leitebahnen horizontal laufen,

7 Leiterbahnen zwischen zwei Anodenkontakten im 0,635 mm-Raster

hindurch. Da lässt sich keine einfache Reihenfolge a-b-c-d-e-f-g-h

- a-b-c-d-e-f-g-h einhalten. Die Leiterbahnen auf dem Foto sind

im ca. 45 µm-Raster, also geschätzt bei 15 µm

Abstand nur 30 µm breit. Zur Verkomplizierung der Ansteuerung

kommt hinzu, dass, obwohl 512 Anoden pro Multiplexphase anzusteuern

sind, nur 256 Anodendaten übertragen werden, aber eine externe

Information (das Signal "DTENA") bestimmt, welcher der

256er-Gruppe gemeint ist. Ist halt nicht trivial.

Fazit: Wer das Ganze auf Anhieb verstanden hat ist ein Genie, wer es mit Mühe versteht oder wer sich gar nicht erst die Mühe macht, es zu verstehen, ist normal. Noch viel schwieriger ist allerdings, diese Zusammenhänge aus dem Datenblatt zu erkennen.

Zum Schluss noch der VHDL-Code im FPGA, der für die ganze Entwirrung der Adressierung sorgt. Er könnte vielleicht auch zum Verständnis beitragen, vielleicht auch nur zur Verwirrung. Angenommen ist ein Bildwiederholspeicher, der die Pixeldaten Pixel für Pixel, Zeile für Zeile unter fortlaufenden Adressen "RAMAddress" (8 LSBits für 256 Pixel pro Zeile, 6 MSBits für 64 Zeilen = insgesamt 14 Bit) gespeichert hat.

Gleichzeitig läuft ein Adresszähler "CounterAddress" (8 LSBits für 256 Pixel pro "Doppel-Halbblock", 6 MSBits für 64 "Doppel-Halbblöcke" = insgesamt 14 Bit). Das Ummappen der Adresszählerbits "CounterAddress" auf die RAM-Adressen "RAMAddress" geht z. B. mit folgendem Code:

A(3) <= CounterAddress(9) xnor (CounterAddress(8) and CounterAddress(1)); A(4) <= CounterAddress(10) xnor (CounterAddress(9) and A(3)); A(5) <= CounterAddress(11) xnor (CounterAddress(10) and A(4)); A(6) <= CounterAddress(12) xnor (CounterAddress(11) and A(5)); RAMAddress(0) <= CounterAddress(0) xor CounterAddress(8); RAMAddress(1) <= CounterAddress(1) xnor CounterAddress(8); RAMAddress(2) <= CounterAddress(1); RAMAddress(3) <= A(3); RAMAddress(4) <= CounterAddress(10) xnor (CounterAddress(9) and A(3)); RAMAddress(5) <= CounterAddress(11) xnor (CounterAddress(10) and A(4)); RAMAddress(6) <= CounterAddress(12) xnor (CounterAddress(11) and A(5)); RAMAddress(7) <= CounterAddress(13) xnor (CounterAddress(12) and A(6)); RAMAddress(8) <= CounterAddress(2); RAMAddress(9) <= CounterAddress(3); RAMAddress(10) <= CounterAddress(4); RAMAddress(11) <= CounterAddress(5); RAMAddress(12) <= CounterAddress(6); RAMAddress(13) <= CounterAddress(7);

Der Code, um alle anderen Signale zu erzeugen, ist hier nicht gezeigt. Es geht mir hier nur um das komplexe Adressmapping.

Das VFD hat einen blau-grünen Phosphor und wenn es beleuchtet wird, sinkt der Kontrast nicht allzusehr. Die Farbe ist mit der von modernen Oszilloskopröhren vergleichbar während der Kontrast besser ist. Dennoch kann er durch Farbfilter verbessert werden. Das folgende Foto zeigt 4 Filterscheiben als Beispiel. Diese "Plexiglas®"-Scheiben der Fa. Röhm sind 3 mm stark.

(Anklicken für eine vergrößerte Ansicht)

Von links nach rechts:

Es ist steckt schon schon eine ganze Menge mehr im DPLCM als "noch ein weiteres, hübsches Aussteuerungsmessgerät".

"Digital Peak Level" bedeutet, dass der Spitzenwert des Digitalsignals angezeigt wird. Es gibt Standards für Aussteuerungsmessgeräte, z. B. für VU-Meter oder die DIN 45406 für die professionelleren sogenannte "Peak Program Meter" (PPM), die prinzipiell auch Spitzenwertmessgeräte sind. Aber diese Geräte haben ganz bewusst eine endliche Anstiegszeit von wenigen Millisekunden, während beim DPLCM zum Erreichen des Spitzenwert ein einziges Sample genügt. Damit sind die Zielsetzungen des DPLCMs und eines PPMs unterschiedlich: Das DPLCM soll einen digitalen Audiodatenstrom überwachen und die Reserve bis zum digitalen Clipping anzeigen. Alles unter 0 dB FS (Full Scale, Vollaussteuerung) ist ok, alles darüber kann nicht akzeptiert werden. Für ein PPM würde eine andere Konstruktion gebraucht werden: So müsste die Skala z. B. auch weit in den übersteuerungsbereich reichen können und, wie gesagt, die Ansprechzeit anders sein.

Die zweite wichtige Messung ist die des Korrelationsgrads, oder kurz: der "Korrelation". Stark vereinfacht: Die Korrelation stellt ein Maß an Gemeinsamkeiten zwischen zwei Signalen, hier den beiden Stereokanälen, dar. Zwei identische Signale, auch wenn sie unterschiedliche Pegel haben, haben einen Korrelationsgrad von +1 (+100%), zwei gegenphasige Signale -1 (-100%), Signale aus zwei völlig unabhängigen Quellen 0 (0%).

Gelegentlich wird mit der Korrelationsmessung die Monotauglichkeit eines Stereosignals beurteilt, aber das ist ein sehr unsicheres Verfahren: Normalerweise rechnet man bei Monotauglichkeit mit einer Korrelation von ca. 50% oder mehr. Gegenphasige Signalanteile einer Quelle in den beiden Stereokanäle können sich teilweise oder ganz beim Zusammenführen zu einem Monosignal auslöschen. Das hört sich das schlecht an und ist durch eine geringe Korrelation erkennbar. Wenn aber z. B. das Stereosignal durch zwei weit auseinander stehenden Mikros (= weitgehend unabhängige Quellen) erzeugt wird, ist die Korrelation ebenfalls gering, aber deswegen ist die Monotauglichkeit trotzdem nicht geringer.

Das DPLCM ist mit weiteren Funktionen ausgestattet, die ich hier nicht näher erläutern will. Falls es interessant ist: Das habe ich in dem englischsprachigen Artikel "A VFD-equipped Digital Audio Peak Level and Correlation Meter with many Extra Functions" getan. Deshalb hier nur die übersicht der Eigenschaften des DPLCM-VFDs in Stichworten:

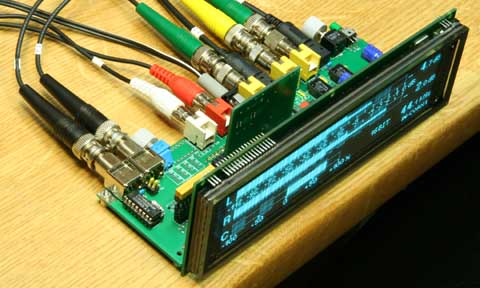

Rückansicht des DPLCM-VFD, mit montiertem und angeschlossenem Audio-I/O-Modul. Von links nach rechts: